Toshiba представила на Симпозиуме по большим интегральным схемам (VLSI Circuits) 32-гигабитный чип NAND flash-памяти с многоуровневыми ячейками (MLC), размещенными в вертикальном положении. Такая структура имеет трехмерный вид, и поэтому ее называют 3D flash-памятью.

32-гигабитный чип P-BiCS (Pipe-shaped Bit Cost Scalable) включает 16 уровней ячеек, каждая из которых способна хранить 2 бита информации. Чип создан по нормам 60-нм техпроцесса и имеет размеры 10,11 х 15,52 мм. Рабочая поверхность ячейки на 1 бит составляет 0,00082 мкм2, это меньше, чем у 32-нм чипов NAND flash-памяти, производство которых будет запущено уже в этом году.

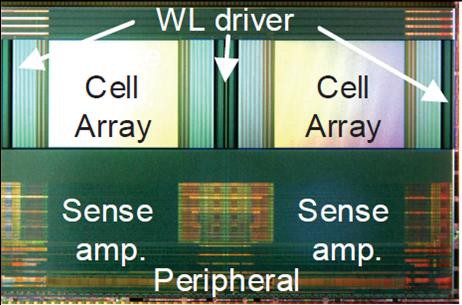

Массив ячеек 3D flash-памяти

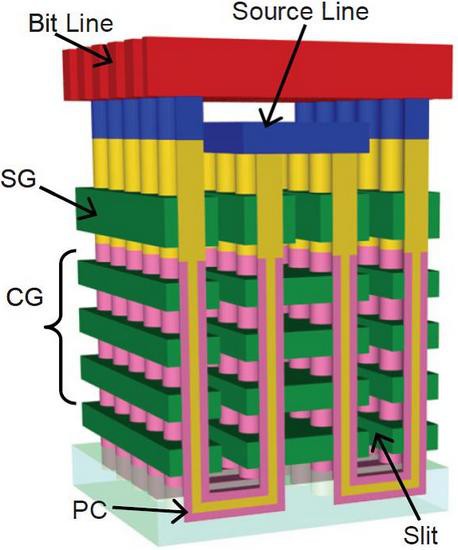

Чип P-BiCS является продвинутым вариантом BiCS — 3D-памяти NAND flash, которую Toshiba разрабатывала с 2007 г. В BiCS реализована технология многоуровневой организации ячеек памяти, это стало возможным за счет:

-

поочередной укладки пленки электрода затвора с пленкой диэлектрика;

-

группирования ячеек таким образом, чтобы между уровнями создавалось сквозное отверстие;

-

встраивания канала поликристаллического кремния.

В BiCS ячейки соединялись в линейную (в форме буквы I) последовательность, в P-BiCS группа соединенных последовательно ячеек имеет форму буквы U.

Такой способ группирования ячеек имеет два больших преимущества по сравнению с I-последовательностью.

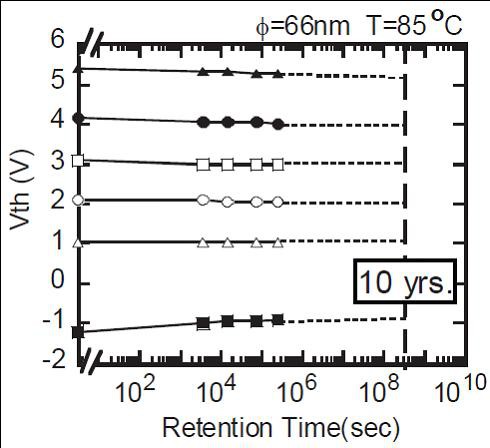

Во-первых, таким образом усиливаются свойства изолирующей пленки, и улучшается способность ячеек сохранять данные.

Данные в 3D-памяти могут храниться на протяжении 10 лет

В BiCS изолирующая пленка, выложенная на стенке с одной стороны туннеля, повреждается в процессе работы, что приводит к ухудшению запоминающих свойств чипа. Toshiba еще в 2007 объявила, что ей удалось сократить повреждение за счет смены материала для туннельной изолирующей пленки: вместо диоксида кремния, был применен нитрид кремния. Однако, новый материал так и не обеспечил достаточный уровень запоминающих свойств для 3D flash-памяти.

Во-вторых, благодаря улучшенной работе линии истока транзистора быстрее происходят операции чтения/записи данных. В BiCS, чипе с I-образной последовательностью ячеек, переключающий транзистор (selection transistor) и линия истока расположены в нижней части последовательности.

В P-BiCS, где ячейки организованы в U-образную последовательность, переключающий транзистор и линия истока располагаются в верхней части последовательности. Таким образом, при последовательном соединении ячеек ни переключающий транзистор, ни линия истока не подвергаются высокотемпературному воздействию (около 1000°C). В результате, уменьшается число ошибок при чтении.

Для линии истока транзистора можно использовать металлические материалы, поэтому скорость записи у P-BiCS чипов выше по сравнению с BiCS. В BiCS в качестве линии истока транзистора используется диффузионный слой, который имеет тенденцию к высокому сопротивлению. Высокое сопротивление линии истока транзистора увеличивает колебания порогового напряжения в массиве ячеек, вследствие чего снижается скорость записи.

Разработчики чипа P-BiCS собираются внедрить массовое производство 3D flash-памяти NAND через 2-3 года. Данная технология позволит изготавливать высокоемкие чипы NAND flash-памяти без необходимости дальнейшей миниатюризации технорм производства.