Следующее поколение мобильной вычислительной электроники будет производиться по 20-нм нормам.

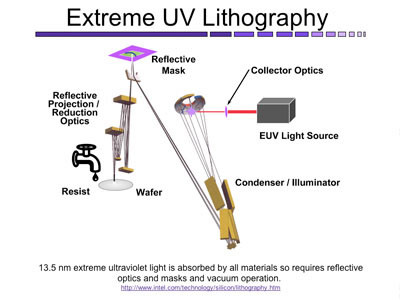

Две вещи идут в различных направлениях — увеличение производительности и снижение энергопотребления. Пользователи хотят, чтобы их устройства были способны на большее, работали быстрее, но без повышения энергопотребления. Это требует новых технологий масштабирования транзисторов и высокоинтегрированного взаимодействия дизайна и литографического производства. На повестке дня стоят: прогресс в разработке транзисторных устройств, расширенной иммерсионной 20-нм литографии и дальнейшее совершенствование литографии в крайнем ультрафиолетовом диапазоне.

20-нм техпроцесс Samsung использует технологию bulk CMOS (комплементарный металлооксидный полупроводник на монолитной подложке), 12 металлических слоёв, медные соединители, диэлектрики со сверхмалым значением диэлектрической постоянной (ultra-low K), стрессоры и HKMG-транзисторы с металлическим затвором и изоляционным слоем с высокой диэлектрической постоянной. Вначале Samsung намерена освоить 20-нм технологию LP, предназначенную для изготовления чипов с низким энергопотреблением.

Во время конференции Common Platform Technology Forum доктор Д.К. Сон (D.K. Sohn), вице-президент центра исследований и разработки в Samsung Electronics, представил технологию 20-нм производства. Компания предполагает, что во второй половине 2012 года удастся довести технологию до стадии рискованного производства, а в первой четверти 2013 года — обеспечить раннее производство. По словам господина Сона, уменьшение норм после 80 нм требует каждый раз серьёзных инноваций. Нет прямого пути перехода с 28-нм на 20-нм нормы.

Он указал на то, что 20-нм нормы LP призваны обеспечить новый уровень производительности мобильных устройств при сохранении низкой стоимости, причём сообщил, что тесное сотрудничество в рамках альянса Common Platform будет продолжаться между R&D-отделами компаний, чтобы предоставить крепкий и жизнеспособный процесс производства, пишет 3Dnews.RU